#include "../eth/eth.h"Go to the source code of this file.

Defines | |

| #define | emacETHADDR0 uipMAC_ADDR0 |

| #define | emacETHADDR1 uipMAC_ADDR1 |

| #define | emacETHADDR2 uipMAC_ADDR2 |

| #define | emacETHADDR3 uipMAC_ADDR3 |

| #define | emacETHADDR4 uipMAC_ADDR4 |

| #define | emacETHADDR5 uipMAC_ADDR5 |

| #define | NUM_RX_FRAG 4 |

| #define | NUM_TX_FRAG 2 |

| #define | ETH_FRAG_SIZE 1536 |

| #define | ETH_MAX_FLEN 1536 |

| #define | RX_DESC_BASE 0x7FE00000 |

| #define | RX_STAT_BASE (RX_DESC_BASE + NUM_RX_FRAG*8) |

| #define | TX_DESC_BASE (RX_STAT_BASE + NUM_RX_FRAG*8) |

| #define | TX_STAT_BASE (TX_DESC_BASE + NUM_TX_FRAG*8) |

| #define | RX_BUF_BASE (TX_STAT_BASE + NUM_TX_FRAG*4) |

| #define | TX_BUF_BASE (RX_BUF_BASE + NUM_RX_FRAG*ETH_FRAG_SIZE) |

| #define | RX_DESC_PACKET(i) (*(unsigned int *)(RX_DESC_BASE + 8*i)) |

| #define | RX_DESC_CTRL(i) (*(unsigned int *)(RX_DESC_BASE+4 + 8*i)) |

| #define | RX_STAT_INFO(i) (*(unsigned int *)(RX_STAT_BASE + 8*i)) |

| #define | RX_STAT_HASHCRC(i) (*(unsigned int *)(RX_STAT_BASE+4 + 8*i)) |

| #define | TX_DESC_PACKET(i) (*(unsigned int *)(TX_DESC_BASE + 8*i)) |

| #define | TX_DESC_CTRL(i) (*(unsigned int *)(TX_DESC_BASE+4 + 8*i)) |

| #define | TX_STAT_INFO(i) (*(unsigned int *)(TX_STAT_BASE + 4*i)) |

| #define | RX_BUF(i) (RX_BUF_BASE + ETH_FRAG_SIZE*i) |

| #define | TX_BUF(i) (TX_BUF_BASE + ETH_FRAG_SIZE*i) |

| #define | MAC1_REC_EN 0x00000001 |

| #define | MAC1_PASS_ALL 0x00000002 |

| #define | MAC1_RX_FLOWC 0x00000004 |

| #define | MAC1_TX_FLOWC 0x00000008 |

| #define | MAC1_LOOPB 0x00000010 |

| #define | MAC1_RES_TX 0x00000100 |

| #define | MAC1_RES_MCS_TX 0x00000200 |

| #define | MAC1_RES_RX 0x00000400 |

| #define | MAC1_RES_MCS_RX 0x00000800 |

| #define | MAC1_SIM_RES 0x00004000 |

| #define | MAC1_SOFT_RES 0x00008000 |

| #define | MAC2_FULL_DUP 0x00000001 |

| #define | MAC2_FRM_LEN_CHK 0x00000002 |

| #define | MAC2_HUGE_FRM_EN 0x00000004 |

| #define | MAC2_DLY_CRC 0x00000008 |

| #define | MAC2_CRC_EN 0x00000010 |

| #define | MAC2_PAD_EN 0x00000020 |

| #define | MAC2_VLAN_PAD_EN 0x00000040 |

| #define | MAC2_ADET_PAD_EN 0x00000080 |

| #define | MAC2_PPREAM_ENF 0x00000100 |

| #define | MAC2_LPREAM_ENF 0x00000200 |

| #define | MAC2_NO_BACKOFF 0x00001000 |

| #define | MAC2_BACK_PRESSURE 0x00002000 |

| #define | MAC2_EXCESS_DEF 0x00004000 |

| #define | IPGT_FULL_DUP 0x00000015 |

| #define | IPGT_HALF_DUP 0x00000012 |

| #define | IPGR_DEF 0x00000012 |

| #define | CLRT_DEF 0x0000370F |

| #define | SUPP_SPEED 0x00000100 |

| #define | SUPP_RES_RMII 0x00000800 |

| #define | TEST_SHCUT_PQUANTA 0x00000001 |

| #define | TEST_TST_PAUSE 0x00000002 |

| #define | TEST_TST_BACKP 0x00000004 |

| #define | MCFG_SCAN_INC 0x00000001 |

| #define | MCFG_SUPP_PREAM 0x00000002 |

| #define | MCFG_CLK_SEL 0x0000001C |

| #define | MCFG_RES_MII 0x00008000 |

| #define | HOST_CLK_BY_20 0x00000018 |

| #define | MCMD_READ 0x00000001 |

| #define | MCMD_SCAN 0x00000002 |

| #define | MII_WR_TOUT 0x00050000 |

| #define | MII_RD_TOUT 0x00050000 |

| #define | MADR_REG_ADR 0x0000001F |

| #define | MADR_PHY_ADR 0x00001F00 |

| #define | MIND_BUSY 0x00000001 |

| #define | MIND_SCAN 0x00000002 |

| #define | MIND_NOT_VAL 0x00000004 |

| #define | MIND_MII_LINK_FAIL 0x00000008 |

| #define | CR_RX_EN 0x00000001 |

| #define | CR_TX_EN 0x00000002 |

| #define | CR_REG_RES 0x00000008 |

| #define | CR_TX_RES 0x00000010 |

| #define | CR_RX_RES 0x00000020 |

| #define | CR_PASS_RUNT_FRM 0x00000040 |

| #define | CR_PASS_RX_FILT 0x00000080 |

| #define | CR_TX_FLOW_CTRL 0x00000100 |

| #define | CR_RMII 0x00000200 |

| #define | CR_FULL_DUP 0x00000400 |

| #define | SR_RX_EN 0x00000001 |

| #define | SR_TX_EN 0x00000002 |

| #define | TSV0_CRC_ERR 0x00000001 |

| #define | TSV0_LEN_CHKERR 0x00000002 |

| #define | TSV0_LEN_OUTRNG 0x00000004 |

| #define | TSV0_DONE 0x00000008 |

| #define | TSV0_MCAST 0x00000010 |

| #define | TSV0_BCAST 0x00000020 |

| #define | TSV0_PKT_DEFER 0x00000040 |

| #define | TSV0_EXC_DEFER 0x00000080 |

| #define | TSV0_EXC_COLL 0x00000100 |

| #define | TSV0_LATE_COLL 0x00000200 |

| #define | TSV0_GIANT 0x00000400 |

| #define | TSV0_UNDERRUN 0x00000800 |

| #define | TSV0_BYTES 0x0FFFF000 |

| #define | TSV0_CTRL_FRAME 0x10000000 |

| #define | TSV0_PAUSE 0x20000000 |

| #define | TSV0_BACK_PRESS 0x40000000 |

| #define | TSV0_VLAN 0x80000000 |

| #define | TSV1_BYTE_CNT 0x0000FFFF |

| #define | TSV1_COLL_CNT 0x000F0000 |

| #define | RSV_BYTE_CNT 0x0000FFFF |

| #define | RSV_PKT_IGNORED 0x00010000 |

| #define | RSV_RXDV_SEEN 0x00020000 |

| #define | RSV_CARR_SEEN 0x00040000 |

| #define | RSV_REC_CODEV 0x00080000 |

| #define | RSV_CRC_ERR 0x00100000 |

| #define | RSV_LEN_CHKERR 0x00200000 |

| #define | RSV_LEN_OUTRNG 0x00400000 |

| #define | RSV_REC_OK 0x00800000 |

| #define | RSV_MCAST 0x01000000 |

| #define | RSV_BCAST 0x02000000 |

| #define | RSV_DRIB_NIBB 0x04000000 |

| #define | RSV_CTRL_FRAME 0x08000000 |

| #define | RSV_PAUSE 0x10000000 |

| #define | RSV_UNSUPP_OPC 0x20000000 |

| #define | RSV_VLAN 0x40000000 |

| #define | FCC_MIRR_CNT 0x0000FFFF |

| #define | FCC_PAUSE_TIM 0xFFFF0000 |

| #define | FCS_MIRR_CNT 0x0000FFFF |

| #define | RFC_UCAST_EN 0x00000001 |

| #define | RFC_BCAST_EN 0x00000002 |

| #define | RFC_MCAST_EN 0x00000004 |

| #define | RFC_UCAST_HASH_EN 0x00000008 |

| #define | RFC_MCAST_HASH_EN 0x00000010 |

| #define | RFC_PERFECT_EN 0x00000020 |

| #define | RFC_MAGP_WOL_EN 0x00001000 |

| #define | RFC_PFILT_WOL_EN 0x00002000 |

| #define | WOL_UCAST 0x00000001 |

| #define | WOL_BCAST 0x00000002 |

| #define | WOL_MCAST 0x00000004 |

| #define | WOL_UCAST_HASH 0x00000008 |

| #define | WOL_MCAST_HASH 0x00000010 |

| #define | WOL_PERFECT 0x00000020 |

| #define | WOL_RX_FILTER 0x00000080 |

| #define | WOL_MAG_PACKET 0x00000100 |

| #define | INT_RX_OVERRUN 0x00000001 |

| #define | INT_RX_ERR 0x00000002 |

| #define | INT_RX_FIN 0x00000004 |

| #define | INT_RX_DONE 0x00000008 |

| #define | INT_TX_UNDERRUN 0x00000010 |

| #define | INT_TX_ERR 0x00000020 |

| #define | INT_TX_FIN 0x00000040 |

| #define | INT_TX_DONE 0x00000080 |

| #define | INT_SOFT_INT 0x00001000 |

| #define | INT_WAKEUP 0x00002000 |

| #define | PD_POWER_DOWN 0x80000000 |

| #define | RCTRL_SIZE 0x000007FF |

| #define | RCTRL_INT 0x80000000 |

| #define | RHASH_SA 0x000001FF |

| #define | RHASH_DA 0x001FF000 |

| #define | RINFO_SIZE 0x000007FF |

| #define | RINFO_CTRL_FRAME 0x00040000 |

| #define | RINFO_VLAN 0x00080000 |

| #define | RINFO_FAIL_FILT 0x00100000 |

| #define | RINFO_MCAST 0x00200000 |

| #define | RINFO_BCAST 0x00400000 |

| #define | RINFO_CRC_ERR 0x00800000 |

| #define | RINFO_SYM_ERR 0x01000000 |

| #define | RINFO_LEN_ERR 0x02000000 |

| #define | RINFO_RANGE_ERR 0x04000000 |

| #define | RINFO_ALIGN_ERR 0x08000000 |

| #define | RINFO_OVERRUN 0x10000000 |

| #define | RINFO_NO_DESCR 0x20000000 |

| #define | RINFO_LAST_FLAG 0x40000000 |

| #define | RINFO_ERR 0x80000000 |

| #define | RINFO_ERR_MASK |

| #define | TCTRL_SIZE 0x000007FF |

| #define | TCTRL_OVERRIDE 0x04000000 |

| #define | TCTRL_HUGE 0x08000000 |

| #define | TCTRL_PAD 0x10000000 |

| #define | TCTRL_CRC 0x20000000 |

| #define | TCTRL_LAST 0x40000000 |

| #define | TCTRL_INT 0x80000000 |

| #define | TINFO_COL_CNT 0x01E00000 |

| #define | TINFO_DEFER 0x02000000 |

| #define | TINFO_EXCESS_DEF 0x04000000 |

| #define | TINFO_EXCESS_COL 0x08000000 |

| #define | TINFO_LATE_COL 0x10000000 |

| #define | TINFO_UNDERRUN 0x20000000 |

| #define | TINFO_NO_DESCR 0x40000000 |

| #define | TINFO_ERR 0x80000000 |

| #define | PHY_REG_BMCR 0x00 |

| #define | PHY_REG_BMSR 0x01 |

| #define | PHY_REG_IDR1 0x02 |

| #define | PHY_REG_IDR2 0x03 |

| #define | PHY_REG_ANAR 0x04 |

| #define | PHY_REG_ANLPAR 0x05 |

| #define | PHY_REG_ANER 0x06 |

| #define | PHY_REG_ANNPTR 0x07 |

| #define | PHY_REG_STS 0x10 |

| #define | PHY_REG_MICR 0x11 |

| #define | PHY_REG_MISR 0x12 |

| #define | PHY_REG_FCSCR 0x14 |

| #define | PHY_REG_RECR 0x15 |

| #define | PHY_REG_PCSR 0x16 |

| #define | PHY_REG_RBR 0x17 |

| #define | PHY_REG_LEDCR 0x18 |

| #define | PHY_REG_PHYCR 0x19 |

| #define | PHY_REG_10BTSCR 0x1A |

| #define | PHY_REG_CDCTRL1 0x1B |

| #define | PHY_REG_EDCR 0x1D |

| #define | PHY_FULLD_100M 0x2100 |

| #define | PHY_HALFD_100M 0x2000 |

| #define | PHY_FULLD_10M 0x0100 |

| #define | PHY_HALFD_10M 0x0000 |

| #define | PHY_AUTO_NEG 0x3000 |

| #define | DP83848C_DEF_ADR 0x0100 |

| #define | DP83848C_ID 0x20005C90 |

Functions | |

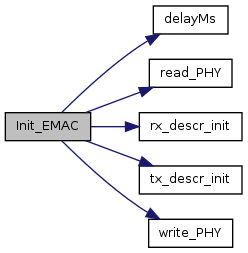

| int | Init_EMAC (void) |

| configure port-pins for use with LAN-controller, reset it and send the configuration-sequence | |

| unsigned short | ReadFrameBE_EMAC (void) |

| void | CopyToFrame_EMAC (void *Source, unsigned int Size) |

| void | CopyFromFrame_EMAC (void *Dest, unsigned short Size) |

| void | DummyReadFrame_EMAC (unsigned short Size) |

| unsigned short | StartReadFrame (void) |

| void | EndReadFrame (void) |

| unsigned int | CheckFrameReceived (void) |

| void | RequestSend (void) |

| unsigned int | Rdy4Tx (void) |

| void | DoSend_EMAC (unsigned short FrameSize) |

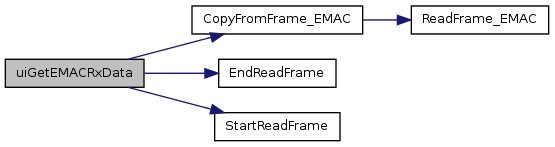

| unsigned int | uiGetEMACRxData (unsigned char *ucBuffer) |

| void | print_PHY_status () |

Define Documentation

| #define RINFO_ERR_MASK |

Value:

(RINFO_FAIL_FILT | RINFO_CRC_ERR | RINFO_SYM_ERR | \ RINFO_LEN_ERR | RINFO_ALIGN_ERR | RINFO_OVERRUN)

Function Documentation

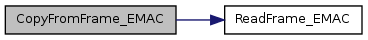

| void CopyFromFrame_EMAC | ( | void * | Dest, | |

| unsigned short | Size | |||

| ) |

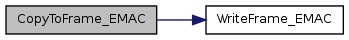

| void CopyToFrame_EMAC | ( | void * | Source, | |

| unsigned int | Size | |||

| ) |

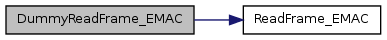

| void DummyReadFrame_EMAC | ( | unsigned short | Size | ) |

| int Init_EMAC | ( | void | ) |

| void print_PHY_status | ( | ) |

1.7.1

1.7.1